+86 18038161406

+86 18038161406

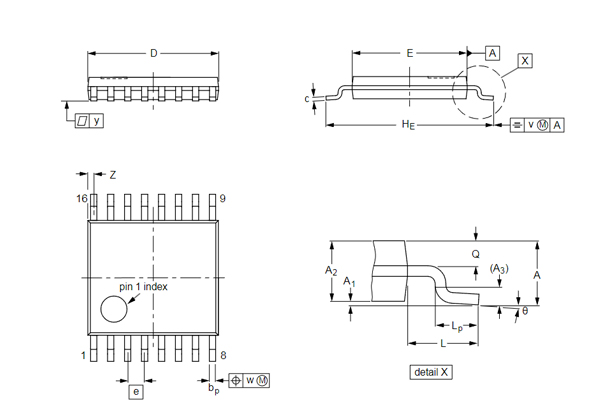

Nexperia 74HC4051PW,118 Analog Switch Overview Datasheet_Functional diagram_Pinning_Package outline 74HC4051PW,118-Package outline

Nexperia's 74HC4051PW,118 is a single-pole eight-throw(SP8T)analog switch,widely used in analog or digital 8:1 multiplexer/demultiplexer designs.This device offers high performance and numerous advantages,making it an ideal choice for modern electronic designs.

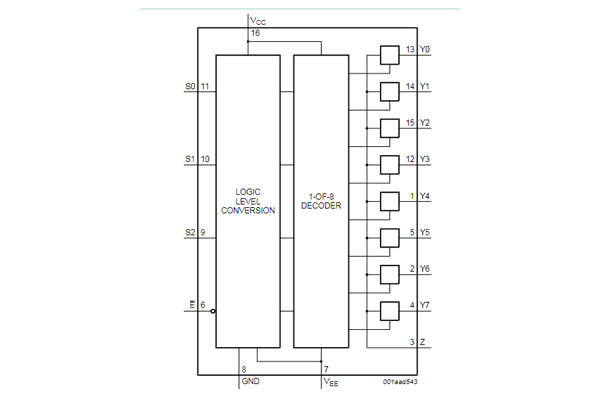

74HC4051PW,118 Functional diagram

Datasheet

Parameter | Value |

Model | 74HC4051PW,118 |

Brand | NEXPERIA |

Package | TSSOP-16 |

Product Type | Multiplexer Switch IC |

RoHS Compliant | Yes |

Mounting Style | SMD/SMT |

Number of Channels | 8 Channels |

Configuration | 1 x 8:1 |

Minimum Power Supply Voltage | 2 V |

Maximum Power Supply Voltage | 10 V |

Maximum On-Resistance | 180 Ohms |

Maximum Turn-On Time | 59 ns |

Maximum Turn-Off Time | 49 ns |

Maximum Dual Supply Voltage | +/- 5 V |

Minimum Operating Temperature | - 40 °C |

Maximum Operating Temperature | + 125 °C |

Bandwidth | 180 MHz |

Power Supply Type | Single Supply, Dual Supply |

Typical Off-Isolation | - 50 dB |

Maximum Supply Current | 0.016 mA |

Operating Supply Voltage | 5 V |

Power Dissipation | 500 mW (1/2 W) |

Propagation Delay Time | 4 ns |

Height | 0.95 mm |

Length | 5.1 mm |

Width | 4.5 mm |

Unit Weight | 173 mg |

Features

Wide Analog Input Voltage Range:-5 V to+5 V,suitable for various application scenarios.

JEDEC 7A Standard Compliance:Ensures high reliability and compatibility.

Low On-Resistance:Typical on-resistance of 80Ω,70Ω,and 60Ωat different voltage ranges,effectively reducing power consumption.

Logic Level Conversion:Facilitates communication between 5 V logic signals and±5 V analog signals,enhancing design flexibility.

Typical Break-Before-Make Mechanism:Ensures reliability during signal switching.

ESD Protection:Complies with HBM JESD22-A114F,MM JESD22-A115-A,and CDM JESD22-C101E standards,providing ESD protection of over 2000 V,200 V,and 1000 V respectively.

Multiple Packaging Options:Meets various application needs.

Wide Operating Temperature Range:Specified from-40°C to+125°C,suitable for harsh environments.

Application

Analog Multiplexing and Demultiplexing

Digital Multiplexing and Demultiplexing

Signal Gating

74HC4051PW,118-Logic symbol

74HC4051PW,118-Pinning

74HC4051PW,118-Package outline