+86 18038161406

+86 18038161406

SOP package characteristics _ size _ process flow

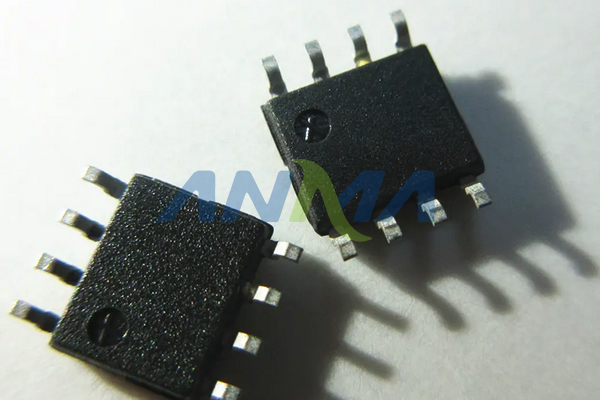

In the field of electronics, "SOP package" refers to the "Small Outline Package"chip packaging technology, SOP is a common form of integrated circuit chip package, which is characterized by small size, few pins and tight arrangement.

The SOP package is suitable for many integrated circuits such as microcontrollers, memories, amplifiers, etc. It is made by packaging the chip in a small package. It protects the chip and provides pin connections by encapsulating the chip in a small-sized plastic or ceramic package.SOP chip packages are usually of two main types:

SOP (Small Outline Package): this is the most common type of SOP package, the pins are located on both sides of the package and are usually inline. It has several variants such as SOP8, SOP16, SOP20, etc. The number indicates the number of pins.SOP packages are usually used for low-power and small-size integrated circuits.

SSOP (Shrink Small Outline Package): SSOP is a further improvement of SOP package, which realizes higher integration through tighter pin layout and size reduction.SSOP package is commonly used in applications with high space requirement, such as mobile devices, wireless communication modules, etc.

SOP chip package features include small size, low cost, easy soldering and compact layout. They are suitable for many application scenarios, ranging from consumer electronics to industrial automation equipment.

SOP Package Dimensions

The following are some of the common dimensions of SOP packaging processes:

SOP8:SOP package with 8 pins, common size is about 3.9 mm x 4.9 mm.

SOP16:SOP package with 16 pins, common size is about 6.5 mm x 10.2 mm.

SOP20: SOP package with 20 pins, common size is about 7.8 mm x 12.8 mm.

These dimensions are just some common examples and do not represent the size range of all SOP chip packages. Actual package dimensions may vary depending on the type of chip package, manufacturer, and application requirements. If the exact dimensions of a specific chip are required, it is recommended to refer to the chip's datasheet or PDF document for detailed information.

SOP Package Characteristics

SOP chip packages have the following key features:

Small size: Typically have small dimensions, making them suitable for compact electronic devices and applications. Compared to other package types, SOP packages are able to accommodate more functions and pins in a limited space.

Fewer pins: The number of pins is relatively small, usually between a few and dozens. This makes SOP chip packages simpler and easier to lay out and solder.

Tight pin arrangement: Pins are usually arranged tightly to minimize package size. The dense layout of the pins helps to improve the integration and performance of the chip.

Surface Mount Technology: It is a Surface Mount Technology (SMT) package in which the chip is soldered to a printed circuit board (PCB) through the surface of the pins. This technology provides higher reliability, better electrical performance and faster production speeds.

Low Cost: Typically has a low manufacturing cost, making it a cost-effective packaging option for a wide range of applications such as consumer electronics, communications equipment and industrial applications.

Widely used: Due to its small size, simplified design and low-cost features, SOP packages are widely used in a variety of integrated circuits such as microcontrollers, memories, amplifiers, sensors, and more.

It is important to note that SOP packages are small in size, and in high power or high frequency applications, it may be necessary to use a larger package to meet the demand. Therefore, when selecting a package type, it needs to be evaluated and selected based on specific application needs and performance requirements.

SOP Packaging Process

The SOP packaging process is a common packaging technique used to encapsulate an integrated circuit chip in a small-sized plastic or ceramic package to protect the chip and provide pin connections. The following are the general process steps for SOP chip packaging:

Chip Preparation : Chip preparation is the first step in the packaging process. This includes testing, sequencing, and dicing the chip to obtain a chip that meets the requirements.

Package Substrate Preparation: The package substrate is the carrier that carries the chip and provides the pin connections. The substrate is usually made of ceramic or plastic material and is surface treated to improve solder quality and reliability.

Pin Mounting: On the package substrate, chip pins are precisely mounted on the corresponding pads or balls on the substrate by automated equipment. Pin mounting can be achieved using solder paste or other soldering materials.

Soldering: The pins are soldered to the pads or balls to form a solid connection. The soldering process can be performed by hot air flow, infrared heating, reflow or wave soldering.

Cleaning and Testing: After soldering is complete, cleaning is performed to remove any residue and the packaged chip is tested. Testing can include functional testing, electrical characterization testing, temperature testing, etc. to ensure the quality and performance of the packaged chip.

Package encapsulation body encapsulation: The package encapsulation body (package shell or package cover) will cover the entire package area to protect the chip and pins. The package body is usually made of plastic or ceramic material and fixed by adhesive or soldering technology.

Marking and Packaging: Completed packaged chips are marked for identification in subsequent use. The chip will then be packaged appropriately for storage, transportation and use.

It is important to note that specific SOP chip packaging processes may vary depending on the manufacturer and type of package. Each manufacturer may employ its own unique process steps and techniques to meet specific product requirements and quality standards. As a result, there may be slight variations in specific manufacturing processes.

SOP Package Advantages and Disadvantages

SOP chip packages have the following advantages and disadvantages:

Advantages:

Small size: has a small size for space-constrained electronic devices and applications. It allows for higher levels of integration, enabling more functionality to be realized in limited space.

Fewer pins: Typically has a smaller number of pins, making the layout and soldering process simpler and easier.

Cost-effective: SOP packages usually have lower manufacturing costs and are suitable for mass production. It reduces production costs and provides better cost-effectiveness.

Widely used: due to its small size, low manufacturing cost and wide availability, SOP packages are widely used in various integrated circuits such as microcontrollers, memories, amplifiers, sensors, etc.

Disadvantages:

Heat Dissipation Limitations: due to its small size, the SOP package has limited heat dissipation capabilities. For high power applications or chips that require better heat dissipation, other package types may be required.

Current capacity limitation: Due to the small size and dense pinout, SOP packages have limited current capacity. For high current applications, a larger package size may be required to meet the demand.

Frequency Limitations: Due to the tight pin layout, SOP packages have some limitations on the transmission of high frequency signals. For high frequency applications, other package types may be required to meet the requirements.

Differences between SOP and DIP packages

SOP package and DIP (Dual Inline Package) package are two common IC chip package types, they have some differences in structure and application:

Structure: The SOP package is a surface mount package in which the pins of the chip are attached to the surface of a printed circuit board (PCB) by soldering. It has small, flat dimensions and a tight pin layout. While the DIP package is an insertion package, the chip's pins are connected to the PCB through direct insertion. It is characterized by larger size and wider pin spacing.

Pin type: SOP packages usually have a smaller number of pins, usually between 8 and 48. The pins are usually tiny pads or balls of solder. DIP packages, on the other hand, can have more pins, with common pin counts ranging from 8 to more than 40. The pins are inline and usually leaded.

Application Areas: SOP packages are widely used in modern electronic and communication devices, such as smartphones, tablets, digital cameras, etc. Due to their small size, dense pinout, and surface-mount technology, DIP packages are often used in applications requiring greater size and durability, such as industrial controls, automotive electronics, and power equipment, etc. DIP packages are often used in applications requiring greater size and durability, due to their plug-in connection.

Manufacturing Costs: SOP packages typically have lower manufacturing costs and are suitable for mass production and automated manufacturing.DIP packages may have relatively higher manufacturing costs due to the larger pins and plug-in connections.

It is necessary to select the appropriate package type according to the specific application needs and design requirements. For modern electronic devices with space constraints, SOP packages are usually more common and suitable. For certain applications requiring greater size and durability, DIP packages may be more appropriate.